Overview

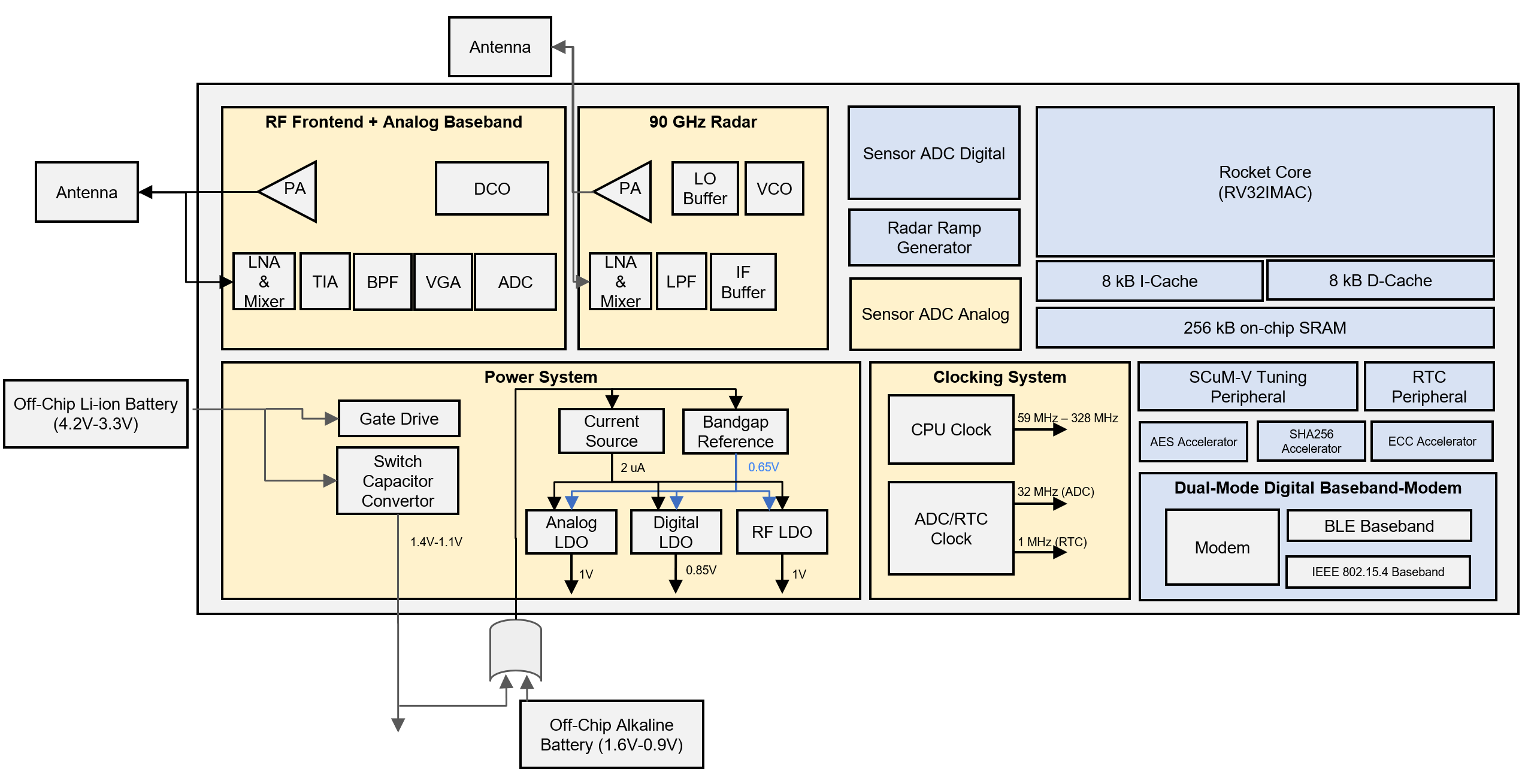

This document describes the Single-Chip Micro Mote V (SCuM-V), a 16nm system-on-chip (SoC) for internet-of-things (IoT) applications, developed as part of the 2022 offering of EE194/EE290C Special Topics in Circuit Design class.

The SoC is designed around the RISC-V 5-stage in-order Rocket processor, generated by the RocketChip generator, embedded in the Chipyard framework. It features a crystal-free design with custom dual-mode IEEE 802.15.4 and Bluetooth Low Energy (BLE) transceiver. The SoC is implemented in the Intel 16 FinFET process.

The SCuM-V chip offers several GPIO pins, a single UART bus, QSPI Flash, and an on-chip, crystal-free RTC with capture and compare registers. This iteration of the chip did not support I2C or an AES accelerator.

SCuM-V23 has several new features introduced over its predecessor SCuM-V22:

- 32-bit Rocket core with cryptography acceleration

- Switched capacitor DC-DC converter cascaded with LDOs

- 90 GHz FMCW radar transmitter

- 18-bit µV-precision ADC

Block Level Diagram + Chip Features

32-bit RISC-V Core

The SoC includes a 32-bit Rocket, which has a high-performance single-issue in-order execution pipeline, with a peak sustainable execution rate of one instruction per clock cycle. The core supports Machine and User privilege modes as well as standard Integer, Multiply, Atomic, Floating-Point and Compressed RISC‑V extensions (RV32IMAFC).

Detailed description of the core is in Chapter 3.

On-Chip Memory System

The Rocket core has a 8kB I and a 256kB scratchpad acting as L2 memory.

Busses

The design includes a system, peripheral, control, and front bus. The Rocket Tile communicates through the system bus to the remaining three buses. The control bus accesses BootROM, PLIC/CLINT, and the debug interface. The frontend bus handles DMA devices.

Interrupts

Two interrupt controllers for handling MMIO are attached to the control bus, the platform level interrupt controller and the core local interrupts. Core local interrupts are used for timer and the software while the PLIC interacts with the peripherals.

Dual-Mode BLE/IEEE 802.15.4 Transceiver

A dual-mode transceiver that supports both Bluetooth Low-Energy and IEEE 802.15.4 modes of operation. In the Bluetooth LE operating mode, the transceiver is capable of sending and receiving BLE Link Layer packets at a rate of 1Msym/s. In IEEE 802.15.4 operating mode, the transceiver sends and receives 802.15.4 PHY packets at 2 Msym/s.

The CPU is able to provide packet payloads to the digital baseband using DMA. Incoming packets will trigger multiple interrupts and provide the packet to the CPU via DMA. Control, status, and tuning registers are exposed to the CPU via MMIO. This includes a large suite of parameters of the transceiver (e.g. radio mode, channel tuning) that are accessed with these memory-mapped registers.